Madan Mohan Malaviya Univ. of Technology, Gorakhpur

# VLSI Design (BEC-41) (Unit-2, Lecture-5)

#### Presented By: Prof. R. K. Chauhan

**Department of Electronics and Communication Engineering**

Madan Mohan Malaviya Univ. of Technology, Gorakhpur

#### **Switching Characteristics of CMOS Inverter**

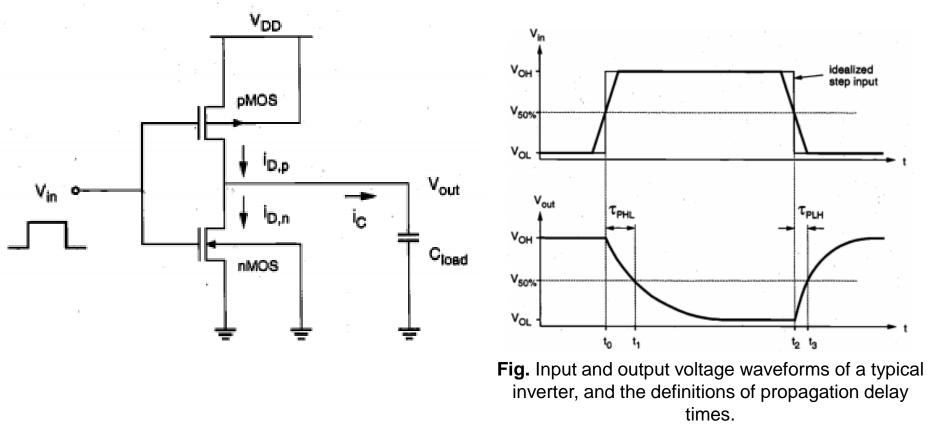

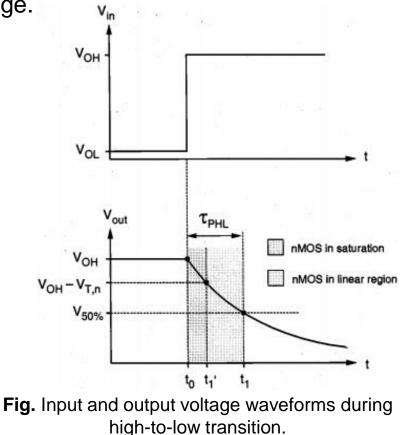

• The propagation delay times  $\tau_{\rm PHL}$  and  $\tau_{\rm PLH}$  are found from Figure as

$$\tau_{\rm PHL}$$

= t<sub>1</sub>- t<sub>0</sub> and  $\tau_{\rm PLH}$  = t<sub>3</sub>- t<sub>2</sub>

# **Switching Characteristics of CMOS Inverter**

- The propagation delay times  $\tau_{\rm PHL}$  and  $\tau_{\rm PLH}$  determine the input-to-output signal delay during the high-to-low and low-to-high transitions of the output, respectively.

- By definition,  $\tau_{PHL}$  is the time delay between the V<sub>50%</sub>-transition of the rising input voltage and the V<sub>50%</sub> -transition of the falling output voltage.

- Similarly,  $\tau_{\rm PLH}$  is defined as the time delay between the V<sub>50%</sub> -transition of the falling input voltage and the V<sub>50%</sub> -transition of the rising output voltage.

• The propagation delay times can be found more accurately by solving the state equation of the output node in the time domain. The differential equation associated with the output node is given below. Note that the capacitance current is also a function of the output voltage.  $v_{in}$

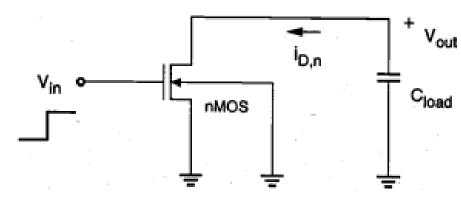

Fig. Equivalent circuit of the CMOS inverter during high-to-low output transition.

• First, consider the NMOS transistor operating in saturation.

$$\begin{split} i_{D,n} &= \frac{k_n}{2} \left( V_{in} - V_{T,n} \right)^2 \\ &= \frac{k_n}{2} \left( V_{OH} - V_{T,n} \right)^2, \qquad for \qquad V_{OH} - V_{T,n} < V_{out} \le V_{OH} \end{split}$$

• the solution equation in the time interval between  $t_o$  and  $t_1$ ', can be found as

$$\int_{t=t_{0}}^{t=t_{1}'} dt = -C_{load} \int_{V_{out}=V_{OH}}^{V_{out}=V_{OH}-V_{T,n}} \left(\frac{1}{i_{D,n}}\right) dV_{out} = -\frac{2C_{load}}{k_{n} \left(V_{OH}-V_{T,n}\right)^{2}} \int_{V_{out}=V_{OH}}^{V_{out}=V_{OH}-V_{T,n}} \int_{V_{out}=V_{OH}}^{V_{out}=V_{OH}-V_{T,n}} dV_{out}$$

• Evaluating this simple integral yields

$$t_{1}' - t_{0} = \frac{2 C_{load} V_{T,n}}{k_{n} \left( V_{OH} - V_{T,n} \right)^{2}}$$

- At t =  $t_1$ ', the output voltage will be equal to ( $V_{DD} V_{T,n}$ ) and the transistor will be at the saturation-linear region boundary.

- Next, consider the NMOS transistor operating in the linear region:

$$i_{D,n} = \frac{k_n}{2} \Big[ 2 \Big( V_{in} - V_{T,n} \Big) V_{out} - V_{out}^2 \Big]$$

=  $\frac{k_n}{2} \Big[ 2 \Big( V_{OH} - V_{T,n} \Big) V_{out} - V_{out}^2 \Big], \quad for \quad V_{out} \le V_{OH} - V_{T,n}$

• The solution of equation in the time interval between  $t_1$ ' and  $t_1$  can be found as

$$\int_{t=t_{1}}^{t=t_{1}} dt = -C_{load} \int_{V_{out}=V_{OH}-V_{T,n}}^{V_{out}=V_{50\%}} \left(\frac{1}{i_{D,n}}\right) dV_{out}$$

$$= -2C_{load} \int_{V_{out}=V_{50\%}}^{V_{out}=V_{50\%}} \left(\frac{1}{k_{n} \left[2\left(V_{OH}-V_{T,n}\right)V_{out}-V_{out}^{2}\right]}\right) dV_{out}$$

$$t_{1} - t_{1}' = \frac{C_{load}}{k_{n} \left( V_{OH} - V_{T,n} \right)} \ln \left( \frac{2 \left( V_{OH} - V_{T,n} \right) - V_{50\%}}{V_{50\%}} \right)$$

Finally, the propagation delay time for high-to-low output transition (T<sub>PHL</sub>) can be found by combining both timing equations:

$$r_{PHL} = \frac{C_{load}}{k_n \left( V_{OH} - V_{T,n} \right)} \left[ \frac{2 V_{T,n}}{V_{OH} - V_{T,n}} + \ln \left( \frac{4 \left( V_{OH} - V_{T,n} \right)}{V_{OH} + V_{OL}} - 1 \right) \right]$$

• For  $V_{OH} = V_{DD}$  and  $V_{OL} = 0$ , as is the case for the CMOS inverter, becomes:

$$\tau_{PHL} = \frac{C_{load}}{k_n \left( V_{DD} - V_{T,n} \right)} \left[ \frac{2 V_{T,n}}{V_{DD} - V_{T,n}} + \ln \left( \frac{4 \left( V_{DD} - V_{T,n} \right)}{V_{DD}} - 1 \right) \right]$$

# Calculation of Delay Times (Continued..)

- In a CMOS inverter, the charge-up event of the output load capacitance for falling input transition is completely analogous to the charge-down event for rising input.

- When the input voltage switches from high (V<sub>OH</sub>) to low (V<sub>OL</sub>), the NMOS transistor is cut off, and the load capacitance is being charged up through the PMOS transistor.

- Following a very similar derivation procedure, the propagation delay time  $\tau_{\rm PI\,H}$  can be found as:

$$\tau_{PLH} = \frac{C_{load}}{k_p \left( V_{OH} - V_{OL} - \left| V_{T,p} \right| \right)} \left[ \frac{2 \left| V_{T,p} \right|}{V_{OH} - V_{OL} - \left| V_{T,p} \right|} + \ln \left( \frac{2 \left( V_{OH} - V_{OL} - \left| V_{T,p} \right| \right)}{V_{OH} - V_{50\%}} - 1 \right) \right]$$

• For  $V_{OH} = V_{DD}$  and  $V_{OL} = 0$ , equation becomes

$$\tau_{PLH} = \frac{C_{load}}{k_p \left( V_{DD} - \left| V_{T,p} \right| \right)} \left[ \frac{2 \left| V_{T,p} \right|}{V_{DD} - \left| V_{T,p} \right|} + \ln \left( \frac{4 \left( V_{DD} - \left| V_{T,p} \right| \right)}{V_{DD}} - 1 \right) \right]$$

Madan Mohan Malaviya Univ. of Technology, Gorakhpur

#### **Calculation of Delay Times (Continued..)**

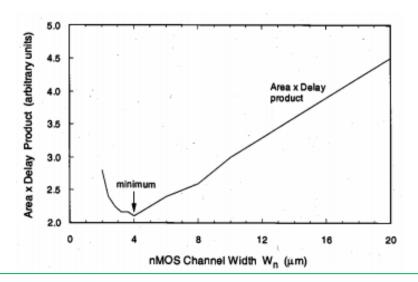

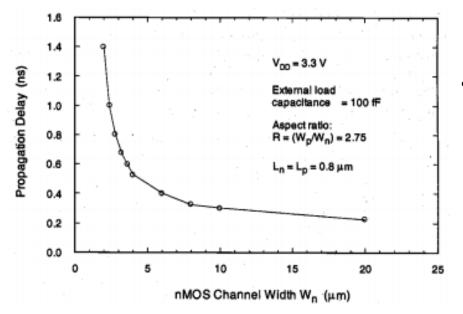

In fact, the increase in silicon area can be viewed as a design trade-off for delay reduction, since the circuit speed improvements are typically obtained at the expense of increased transistor dimensions.  In the following figure, the fallingoutput propagation delay τ<sub>PHL</sub> (obtained from SPICE simulation) is plotted as a function of the NMOS channel width.