Madan Mohan Malaviya Univ. of Technology, Gorakhpur

## VLSI Design (BEC-41) (Unit-2, Lecture-4)

#### Presented By: Prof. R. K. Chauhan

**Department of Electronics and Communication Engineering**

### **CMOS Inverter**

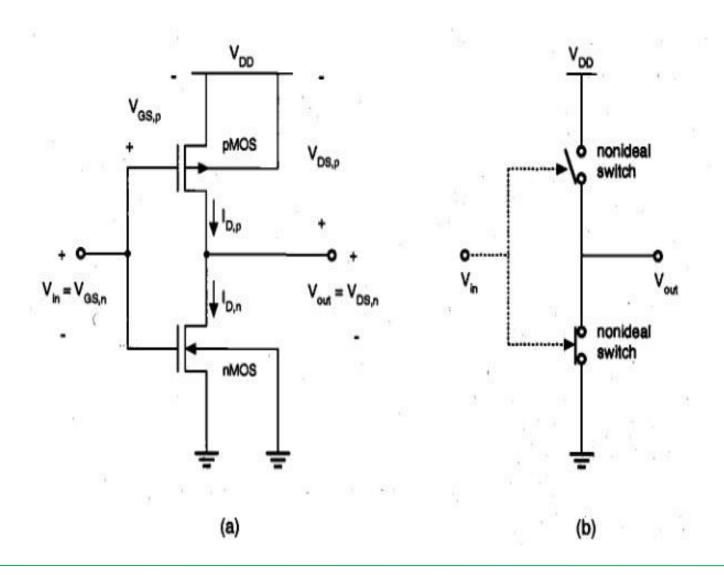

- The CMOS inverter has two important advantages over the other inverter configurations:

- The first and perhaps the most important advantage is that the steady-state power dissipation of the CMOS inverter circuit is virtually negligible, except for small power dissipation due to leakage currents. In all other inverter structures examined so far, a nonzero steady-state current is drawn from the power source when the driver transistor is turned on, which results in a significant DC power consumption.

- The other advantages of the CMOS configuration are that the voltage transfer characteristic (VTC) exhibits a full output voltage swing between 0 V and V<sub>DD</sub>, and that the VTC transition is usually very sharp. Thus, the VTC of the CMOS inverter resembles that of an ideal inverter.

Madan Mohan Malaviya Univ. of Technology, Gorakhpur

### **CMOS Inverter**

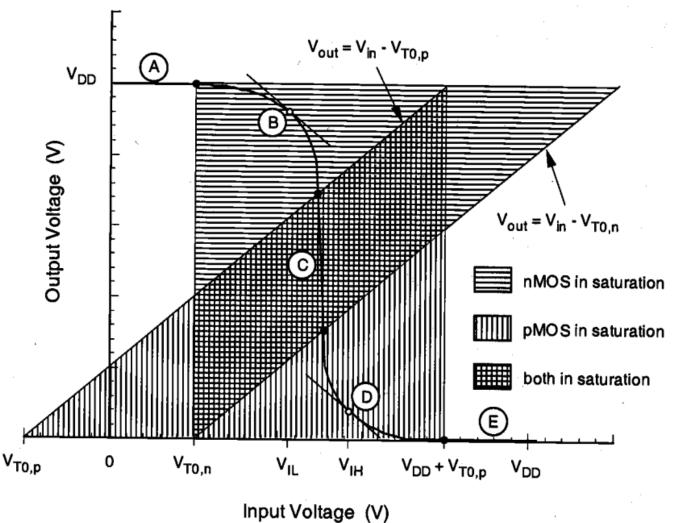

Fig. Operating regions of the nMOS and the pMOS transistors.

#### **CMOS Inverter**

| Region | Vin                     | Vout                  | nMOS       | pMOS       |

|--------|-------------------------|-----------------------|------------|------------|

| A      | < V <sub>T0, n</sub>    | V <sub>OH</sub>       | cut-off    | linear     |

| В      | $V_{IL}$                | high $\approx V_{OH}$ | saturation | linear     |

| C      | V <sub>th</sub>         | V <sub>th</sub>       | saturation | saturation |

| D      | V <sub>IH</sub>         | low $\approx V_{OL}$  | linear     | saturation |

| Ĕ      | $> (V_{DD} + V_{T0,p})$ | V <sub>OL</sub>       | linear     | cut-off    |

- In **Region A**, where Vin<  $V_{T0}$ , the NMOS transistor is cut-off and the output voltage is equal to  $V_{OH} = V_{DD}$ .

- As the input voltage is increased beyond V<sub>T0,n</sub>, (into **Region B**), the NMOS transistor starts conducting in saturation mode and the output voltage begins to decrease. Also note that the critical voltage V<sub>IL</sub> which corresponds to  $(dV_{out}/dV_{in}) = -1$  is located within **Region B**.

- As the output voltage further decreases, the PMOS transistor enters saturation at the boundary of **Region C**. It is seen from figure that the inverter threshold voltage, where V<sub>in</sub>= V<sub>out</sub>, is located in **Region C**.

- When the output voltage V<sub>out</sub>, falls below (Vin V<sub>T0,n</sub>), the NMOS transistor starts to operate in linear mode. This corresponds to **Region D** in figure, where the critical voltage point V<sub>IH</sub> with  $(dV_{out}/dV_{jn}) = -1$  is also located.

- Finally, in Region E, with the input voltage V<sub>in</sub> > (V<sub>DD</sub> + V<sub>T0,p</sub>), the PMOS transistor is cut-off, and the output voltage is V<sub>OL</sub>= 0.

- It has already been established that  $V_{OH} = V_{DD}$  and  $V_{OL} = 0$  for this inverter; thus, we will devote our attention to  $V_{IL}$ ,  $V_{IH}$  and the inverter switching threshold,  $V_{th}$ .

## Calculation of V<sub>IL</sub>

- By definition, the slope of the VTC is equal to (-1), i.e.,  $dV_{out}/dV_{in} = -1$  when the input voltage is  $V_{in} = V_{IL}$ .

- Note that in this case, the NMOS transistor operates in saturation while the PMOS transistor operates in the linear region.

- From  $I_{D,n} = I_{D,p}$ , we obtain the following current equation:

$$\frac{k_n}{2} \cdot \left( V_{GS,n} - V_{T0,n} \right)^2 = \frac{k_p}{2} \cdot \left[ 2 \cdot \left( V_{GS,p} - V_{T0,p} \right) \cdot V_{DS,p} - V_{DS,p}^2 \right]$$

$$\frac{k_n}{2} \cdot (V_{in} - V_{T0,n})^2 = \frac{k_p}{2} \cdot \left[ 2 \cdot (V_{in} - V_{DD} - V_{T0,p}) + (V_{out} - V_{DD}) - (V_{out} - V_{DD})^2 \right]$$

# Calculation of V<sub>IL</sub>

- To satisfy the derivative condition at  $V_{\text{IL}}$  , we differentiate both sides with respect to  $V_{\text{in}}.$

$$k_n \cdot \left(V_{in} - V_{T0,n}\right) = k_p \cdot \left[ \left(V_{in} - V_{DD} - V_{T0,p}\right) \cdot \left(\frac{dV_{out}}{dV_{in}}\right) + \left(V_{out} - V_{DD}\right) - \left(V_{out} - V_{DD}\right) \cdot \left(\frac{dV_{out}}{dV_{in}}\right) \right]$$

• Substituting  $V_{in} = V_{IL}$  and  $(dV_{out} / dV_{in}) = -1$  in above equation, we obtain:

$$V_{IL} = \frac{2 V_{out} + V_{T0,p} - V_{DD} + k_R V_{T0,n}}{1 + k_R}$$

where

$$k_R$$

is defined as:  $k_R = \frac{k}{k}$

р

## Calculation of V<sub>IH</sub>

When the input voltage is equal to V<sub>IH</sub>, the NMOS transistor operates in the linear region, and the PMOS transistor operates in saturation. Applying KCL to the output node, we obtain

$$\frac{k_n}{2} \cdot \left[ 2 \cdot \left( V_{GS,n} - V_{T0,n} \right) \cdot V_{DS,n} - V_{DS,n}^2 \right] = \frac{k_p}{2} \cdot \left( V_{GS,p} - V_{T0,p} \right)^2$$

$$\frac{k_n}{2} \cdot \left[ 2 \cdot \left( V_{in} - V_{T0,n} \right) \cdot V_{out} - V_{out}^2 \right] = \frac{k_p}{2} \cdot \left( V_{in} - V_{DD} - V_{T0,p} \right)^2$$

• Now, differentiate both sides with respect to V<sub>in</sub>:

$$k_{n} \cdot \left[ \left( V_{in} - V_{T0,n} \right) \cdot \left( \frac{dV_{out}}{dV_{in}} \right) + V_{out} - V_{out} \cdot \left( \frac{dV_{out}}{dV_{in}} \right) \right]$$

$$= k_{p} \cdot \left( V_{in} - V_{DD} - V_{T0,p} \right)$$

# Calculation of V<sub>IH</sub>

• Substituting,  $V_{in} = V_{IH}$  and  $(dV_{out}/dV_{in}) = -1$  in above equation, we obtain

$$k_n \cdot (-V_{IH} + V_{T0,n} + 2V_{out}) = k_p \cdot (V_{IH} - V_{DD} - V_{T0,p})$$

$$V_{IH} = \frac{V_{DD} + V_{T0,p} + k_R \cdot (2 V_{out} + V_{T0,n})}{1 + k_R}$$

- Again, this equation must be solved simultaneously with the KCL equation to obtain the numerical values of  $V_{\rm IH}$  and  $V_{\rm out}.$

## Calculation of V<sub>th</sub>

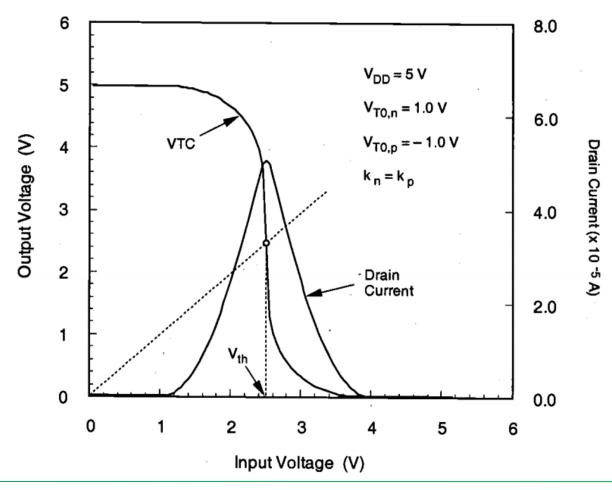

- The inverter threshold voltage is defined as  $V_{th} = V_{th} = V_{out}$ , Since the CMOS inverter exhibits large noise margins and a very sharp VTC transition, the inverter threshold voltage emerges as an important parameter characterizing the DC performance of the inverter.

- For V<sub>in</sub>= V<sub>out</sub>, both transistors are expected to be in saturation mode; hence, we can write the following KCL equation:

$$\frac{k_n}{2} \cdot \left(V_{GS,n} - V_{T0,n}\right)^2 = \frac{k_p}{2} \cdot \left(V_{GS,p} - V_{T0,p}\right)^2$$

$$\frac{k_n}{2} \cdot \left(V_{in} - V_{T0,n}\right)^2 = \frac{k_p}{2} \cdot \left(V_{in} - V_{DD} - V_{T0,p}\right)^2$$

## Calculation of $V_{th}$

• The correct solution for  $V_{in}$  for this equation is:

$$V_{in} \cdot \left(1 + \sqrt{\frac{k_p}{k_n}}\right) = V_{T0,n} + \sqrt{\frac{k_p}{k_n}} \cdot \left(V_{DD} + V_{T0,p}\right)$$

• Finally, the inverter threshold (switching threshold) voltage  $V_{th}$ , is found as

$$V_{th} = \frac{V_{T0,n} + \sqrt{\frac{1}{k_R}} \cdot \left(V_{DD} + V_{T0,p}\right)}{\left(1 + \sqrt{\frac{1}{k_R}}\right)}$$

Madan Mohan Malaviya Univ. of Technology, Gorakhpur

### **CMOS Inverter**

#### Calculation of V<sub>th</sub>

**Fig.** Typical VTC and the power supply current of a CMOS inverter circuit.

## Calculation of V<sub>th</sub>

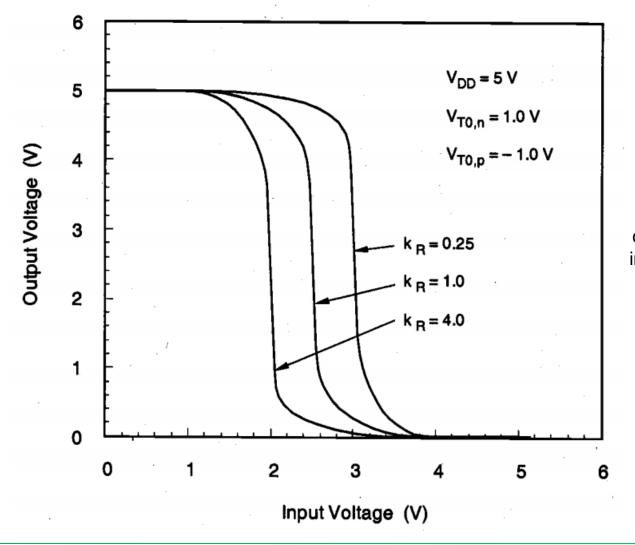

• Now solve for kR that is required to achieve the given  $V_{th}$ :

$$k_{R} = \frac{k_{n}}{k_{p}} = \left(\frac{V_{DD} + V_{T0,p} - V_{th}}{V_{th} - V_{T0,n}}\right)^{2}$$

• Recall that the switching threshold voltage of an ideal inverter is defined as:

$$V_{th, ideal} = \frac{1}{2} \cdot V_{DD}$$

$$\left(\frac{k_n}{k_p}\right)_{ideal} = \left(\frac{0.5 V_{DD} + V_{T0,p}}{0.5 V_{DD} - V_{T0,n}}\right)^2$$

# Calculation of V<sub>th</sub>

For a near-ideal CMOS VTC that satisfies the above condition. Since the • operations of the NMOS and the PMOS transistors of the CMOS inverter are fully complementary, we can achieve completely symmetric inputoutput characteristics by setting the threshold voltages as  $V_{T0} = V_{T0,p} =$  $|V_{T0,p}|$ . This reduces to:

$$\left(\frac{k_n}{k_p}\right)_{\substack{\text{symmetric}\\\text{inverter}}} = 1 \qquad \frac{k_n}{k_p} = \frac{\mu_n C_{ox} \cdot \left(\frac{W}{L}\right)_n}{\mu_p C_{ox} \cdot \left(\frac{W}{L}\right)_p} = \frac{\mu_n \cdot \left(\frac{W}{L}\right)_n}{\mu_p \cdot \left(\frac{W}{L}\right)_p}$$

$$\frac{\frac{W}{L}}{\frac{W}{L}}\right)_p = \frac{\mu_p}{\mu_n} \approx \frac{230 \text{ cm}^2/\text{V}\cdot\text{s}}{580 \text{ cm}^2/\text{V}\cdot\text{s}} \qquad \left(\frac{W}{L}\right)_p \approx 2.5 \left(\frac{W}{L}\right)_n$$

### **CMOS Inverter**

Fig. Voltage transfer characteristics of three CMOS inverters, with different NMOSto-PMOS ratios.