Madan Mohan Malaviya Univ. of Technology, Gorakhpur

## VLSI Design (BEC-41) (Unit-1, Lecture-3)

#### Presented By: Prof. R. K. Chauhan

**Department of Electronics and Communication Engineering**

# **MOSFET operation: linear region**

- The MOSFET consists

- A MOS capacitor, two pn junction adjacent to the channel

- The channel is controlled to the MOS gate

- The carrier (electron in nMOSFET)

- Entering through source, controlling by gate, leaving through drain

- To ensure that both p-n junctions are reverse-biased initially

- The substrate potential is kept lower than the other three terminal potentials

- When  $0 < V_{GS} < V_{T0}$

- G-S region depleted, G-D region depleted

- No current flow

- When  $V_{GS} > V_{T0}$

- Conduction channel formed

- Capable of carrying the drain current

- As V<sub>DS</sub>=0

- I<sub>D</sub>=0

- As  $V_{DS}$ >0 and small

- $I_D$  proportional to  $V_{DS}$

- Flowing from S to D through the conducting channel

- The channel act as a voltage controlled resistor

- The electron velocity much lower than the drift velocity limit

- As V<sub>DS</sub>↑⇒the inversion layer charge and the channel depth at the drain end start to decrease

$V_{G} > V_{T}$

CHANNEL

SUBSTRATE (p-Si)

OXIDE

ò V<sub>B</sub>

$V_s = 0$

SOURCE

(n+)

DEPLETION REGION

V<sub>D</sub> small

I<sub>D</sub>

DRAIN

(n+)

17

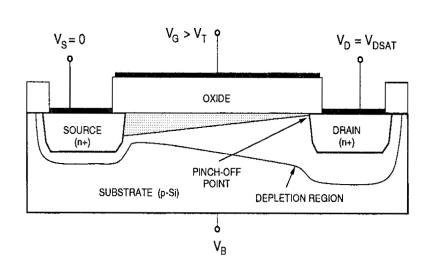

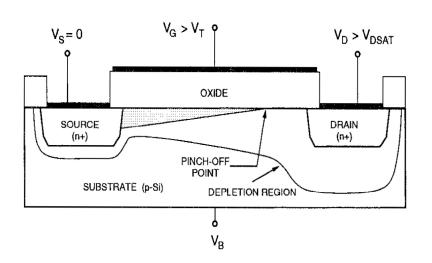

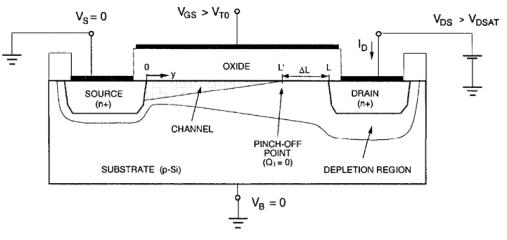

# **MOSFET operation: saturation region**

- For V<sub>DS</sub>=V<sub>DSAT</sub>

- The inversion charge at the drain is reduced to zero

- Pitch off point

- For V<sub>DS</sub>>V<sub>DSAT</sub>

- A depleted surface region forms adjacent to the drain

- As further increases V<sub>DS</sub> ⇒ this depletion region grows toward the source

- The channel-end remains essentially constant and equal to  $V_{\text{DSAT}}$

- The pitch-off (depleted) section

- Absorbing most of the excess voltage drop,  $V_{\text{DS}}\text{-}V_{\text{DSAT}}$

- A high-field forms between the channel-end of the drain boundary

- Accelerating electrons, usually reaching the drift velocity limit

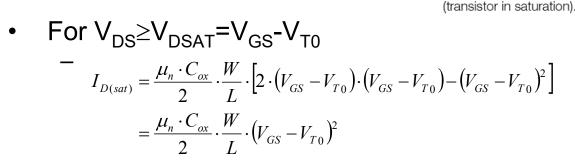

# **MOSFET current-voltage characteristics-gradual**

# channel approximation (GCA)(1)

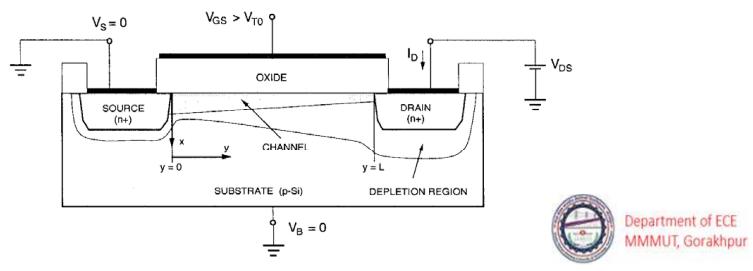

- Considering linear mode operation

- $V_{S}\text{=}V_{B}\text{=}0,$  the  $V_{GS}$  and  $V_{DS}$  are the external parameters controlling the drain current  $I_{D}$

- $-V_{GS} > V_{T0}$  (assume constant through the channel) to create a conducting inversion layer

- Defining

- X-direction: perpendicular to the surface, pointing down into the substrate

- Y-direction: parallel to the surface

- The y=0 is at the source end of the channel

- Channel voltage with respect to the source,  $V_c(y)$

- Assume the electric field  $E_v$  is *dominant* compared with  $E_x$

- This assumption reduced ⇔the current flow in the channel to the y-direction only

- Let  $Q_{I}(y)$  be the total mobile electron charge in the surface inversion layer

- $Q_{I}(y)=-C_{ox}[V_{GS}-Vc(y)-V_{T0}]$

Figure 3.15 Cross-sectional view of an n-channel transistor, operating in linear region.

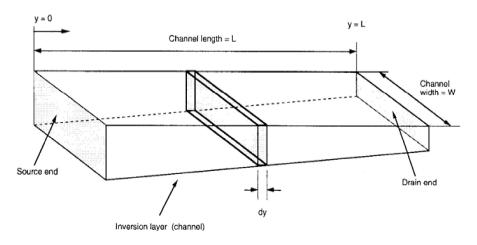

# MOSFET current-voltage characteristics-gradual channel approximation (GCA)(2)

Assumeing that all mobile electrons in the inversion layer has a constant surface mobility  $\mu_n$

$dR = -\frac{dy}{W \cdot \mu_n \cdot Q_I(y)}$ (mimus sign is due to the negative polarity of the inversion layer charge  $Q_I$ )

The electron surface mobility  $\mu_n$  dependents on the doping concentration of the channel region, and its magnitude is typically about one - half of that of the bulk electron mobility

$$dV_{C} = I_{D} \cdot dR = -\frac{I_{D}}{W \cdot \mu_{n} \cdot Q_{I}(y)} \cdot dy$$

$$\int_{0}^{L} I_{D} \cdot dy = -W \cdot \mu_{n} \int_{0}^{V_{DS}} Q_{I}(y) \cdot dV_{C}$$

$$I_{D} \cdot L = W \cdot \mu_{n} \cdot C_{ox} \int_{0}^{V_{DS}} (V_{GS} - V_{C} - V_{T0}) \cdot dV_{C}$$

$$I_{D} = \frac{\mu_{n} \cdot C_{ox}}{2} \cdot \frac{W}{L} \cdot \left[2 \cdot (V_{GS} - V_{T0})V_{DS} - V_{DS}^{2}\right]$$

$$I_{D} = \frac{k}{2} \cdot \frac{W}{L} \cdot \left[2 \cdot (V_{GS} - V_{T0})V_{DS} - V_{DS}^{2}\right] \text{ where } k' = \mu_{n}C_{ox}$$

$$I_{D} = \frac{k}{2} \cdot \left[2 \cdot (V_{GS} - V_{T0})V_{DS} - V_{DS}^{2}\right] \text{ where } k = k' \cdot \frac{W}{L}$$

#### Example 4

For an n-channel MOS transistor with  $\mu_n = 600 \text{ cm}^2/\text{V} \cdot \text{s}$ ,  $C_{ox} = 7 \cdot 10^{-8} \text{ F/cm}^2$ ,  $W = 20 \ \mu\text{m}$ ,  $L = 2 \ \mu\text{m}$  and  $V_{T0} = 1.0 \text{ V}$ , examine the relationship between the drain current and the terminal voltages.

First, calculate the parameter k:

$$k = \mu_n \cdot C_{ox} \cdot \frac{W}{L} = 600 \text{ cm}^2/\text{V} \cdot \text{s} \times 7 \cdot 10^{-8} \text{ F/cm}^2 \times \frac{20 \ \mu\text{m}}{20 \ \mu\text{m}} = 0.42 \text{ mA/V}^2$$

Now, the current-voltage equation (3.34) can be written as follows.

$$I_D = 0.21 \text{ mA/V}^2 \left[ 2 \cdot (V_{GS} - 1.0) \cdot V_{DS} - V_{DS}^2 \right]$$

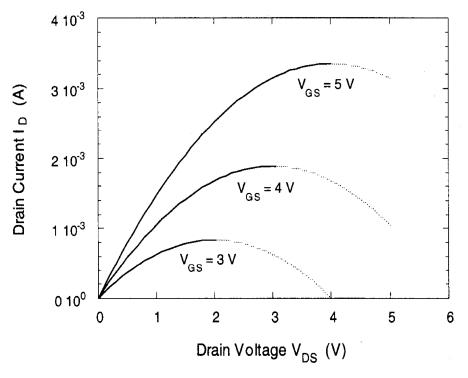

To examine the effect of the gate-to-source voltage and the drain-to-source voltage upon the drain current, we will plot  $I_D$  as a function of  $V_{DS}$ , for different (constant) values of  $V_{GS}$ . It can easily be seen that the second-order current-voltage equation given above produces a set of inverted parabolas for each constant  $V_{GS}$  value.

The drain current-drain voltage curves shown on page 104 reach their peak value for  $V_{DS} = V_{GS} - V_{T0}$ . Beyond this maximum, each curve exhibits a *negative* differential conductance, which is not observed in actual MOSFET current-voltage measurements (section shown by the dashed lines). We must remember now that the drain current equation (3.32) has been derived under the following voltage assumptions,

$$V_{GS} \ge V_{T0}$$

$$V_{GD} = V_{GS} - V_{DS} \ge V_{T0}$$

which guarantee that the entire channel region between the source and the drain is inverted. This condition corresponds to the *linear* operating mode for the MOSFET, which was examined qualitatively in Section 3.4. Hence, the current equation (3.32) is valid only for the linear mode operation. Beyond the linear region boundary, i.e., for  $V_{DS}$  values *larger* than  $V_{GS} - V_{T0}$ , the MOS transistor will be assumed to be in *saturation*. A different current-voltage expression will be necessary for the MOSFET operating in this region.

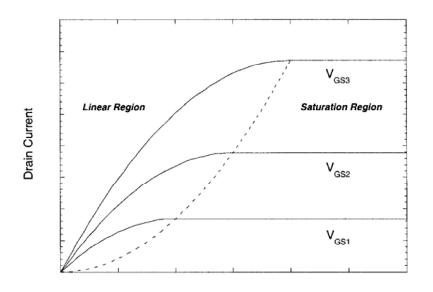

#### **MOSFET current-voltage characteristics-gradual channel approximation (GCA)-saturation region**

Gate Voltage

**Figure 3.18** Drain current of the n-channel MOS transistor as a function of the gate-to-source voltage  $V_{GS}$ , with  $V_{DS} > V_{DSAT}$

**Figure 3.17** Basic current-voltage characteristics of an n-channel MOS transistor.

Drain Voltage

The drain current becomes a function only of V<sub>GS</sub>, beyond the saturation boundary

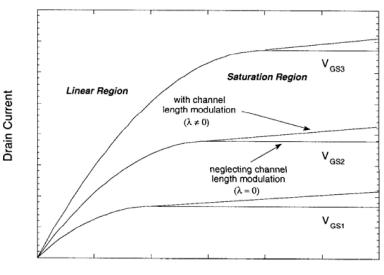

# **Channel length modulation**

The inversion layer charge at the source end of the channel is  $Q_I(y=0) = -C_{ox} \cdot (V_{GS} - V_{T0})$

and the inversion layer charge at the drain end of the channel is  $Q_I(y = L) = -C_{ox} \cdot (V_{GS} - V_{T0} - V_{DS})$

Note that at the edge of saturation,  $V_{DS} = V_{DSAT} = V_{GS} - V_{T0}$

The inversion layer charge at the drain end become very small  $Q_1(y = L) \approx 0$

The effective channel length  $L' = L - \Delta$ -

where  $\Delta \Delta$  is the length of the channel segment with  $Q_I = 0$

$$\begin{split} I_{D(sat)} &= \frac{\mu_n C_{ox}}{2} \cdot \frac{W}{L} \cdot (V_{GS} - V_{T0})^2 \\ I_{D(sat)} &= \left(\frac{1}{1 - \frac{\Delta L}{L}}\right) \frac{\mu_n C_{ox}}{2} \cdot \frac{W}{L} \cdot (V_{GS} - V_{T0})^2 \\ \Delta L \propto \sqrt{V_{DS} - V_{DSAT}} \\ \text{We use } 1 - \frac{\Delta L}{L} \approx 1 - \lambda \cdot V_{DS}, \ \lambda \text{ channel length modulation coeffic} \\ \text{Assuming that } \lambda \lambda_{DS} << 1 \end{split}$$

$$I_{D(sat)} = \frac{\mu_n \cdot C_{ox}}{2} \cdot \frac{W}{L} \cdot \left(V_{GS} - V_{T0}\right)^2 \cdot \left(1 + \lambda V_{DS}\right)$$

Figure 3.19 Channel length modulation in an n-channel MOSFET operation in saturation mode.

Drain Voltage

Figure 3.20 Current-voltage characteristics of an n-channel MOS transistor, including the channel length modulation effect.

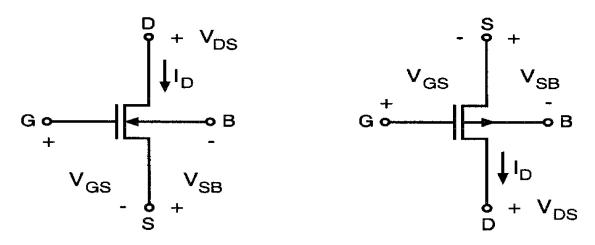

# Substrate bias effect

- The discussion in the previous has been done under the assumption

- The substrate potential is equal to the source potential, i.e.  $V_{SB}=0$

- On the other hand

- the source potential of an nMOS transistor can be larger than the substrate potential, i.e.  $V_{SB} > 0$

$$V_T(V_{SB}) = V_{T0} + \gamma \cdot \left(\sqrt{\left|2\phi_F\right| + V_{SB}} - \sqrt{\left|2\phi_F\right|}\right)$$

$$I_{D(lin)} = \frac{\mu_n \cdot C_{ox}}{2} \cdot \frac{W}{L} \cdot \left[2 \cdot \left(V_{GS} - V_T(V_{SB})\right) V_{DS} - V_{DS}^2\right]$$

$$I_{D(sat)} = \frac{\mu_n \cdot C_{ox}}{2} \cdot \frac{W}{L} \cdot \left(V_{GS} - V_T(V_{SB})\right)^2 \cdot \left(1 + \lambda \cdot V_{DS}\right)$$

n-channel MOSFET

p-channel MOSFET

**Figure 3.21** Terminal voltages and currents of the nMOS and the pMOS transistor.

#### **Current-voltage equation of n-, p-channel MOSFET**

For n - channel MOSFET

$$\begin{split} I_{D} &= 0, \quad \text{for } V_{GS} < V_{T} \\ I_{D(lin)} &= \frac{\mu_{n} \cdot C_{ox}}{2} \cdot \frac{W}{L} \cdot \left[ 2 \cdot \left( V_{GS} - V_{T} \right) V_{DS} - V_{DS}^{2} \right] \text{ for } V_{GS} \ge V_{T} \\ & \text{ and } V_{DS} < V_{GS} - V_{T} \\ I_{D(sat)} &= \frac{\mu_{n} \cdot C_{ox}}{2} \cdot \frac{W}{L} \cdot \left( V_{GS} - V_{T} \right)^{2} \cdot \left( 1 + \lambda \cdot V_{DS} \right) \text{ for } V_{GS} \ge V_{T} \\ & \text{ and } V_{DS} \ge V_{GS} - V_{T} \end{split}$$

For p - channel MOSFET

$$I_{D} = 0, \text{ for } V_{GS} > V_{T}$$

$$I_{D(lin)} = \frac{\mu_{n} \cdot C_{ox}}{2} \cdot \frac{W}{L} \cdot \left[ 2 \cdot \left( V_{GS} - V_{T} \right) V_{DS} - V_{DS}^{2} \right] \text{ for } V_{GS} \le V_{T}$$

and  $V_{DS} > V_{GS} - V_{T}$

$$\mu_{n} \cdot C_{ox} = W \quad (V_{T} - V_{T})^{2} \quad (1 + 2 - V_{T}) \quad (1 + 2 - V_{T}) \quad (1 + 2 - V_{T})^{2}$$

$$I_{D(sat)} = \frac{\mu_n \cdot C_{ox}}{2} \cdot \frac{W}{L} \cdot \left(V_{GS} - V_T\right)^2 \cdot \left(1 + \lambda \cdot V_{DS}\right) \text{ for } V_{GS} \le V_T$$

Department of ECE MMMUT, Gorakhpur

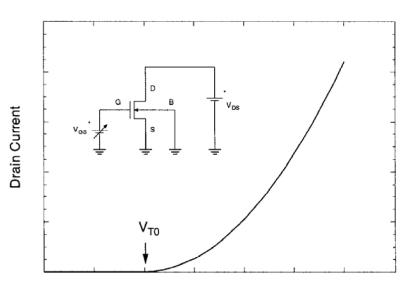

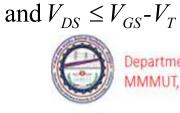

# **Measurement of parameters-** $k_n$ , $V_{T0}$ , and $\gamma$

- The V<sub>SB</sub> is set at a constant value

- The drain current is measured for different values of  $V_{GS}$

- V<sub>DG</sub>=0

- V<sub>DS</sub>>V<sub>GS</sub>-V<sub>T</sub> is always satisfied ⇒ saturation mode

- Neglecting the channel length modulation effect

$$I_{D(sat)} = \frac{k_n}{2} \cdot (V_{GS} - V_{T0})^2, \sqrt{I_D} = \sqrt{\frac{k_n}{2}} \cdot (V_{GS} - V_{T0})$$

– Obtaining the parameters  $k_n,\,V_{T0},\,and\,\gamma$

**Figure 3.22** (a) Test circuit arrangement and (b) measured data for experimental determination of the parameters  $k_{D}$ ,  $V_{T0}$ , and  $\gamma$ .

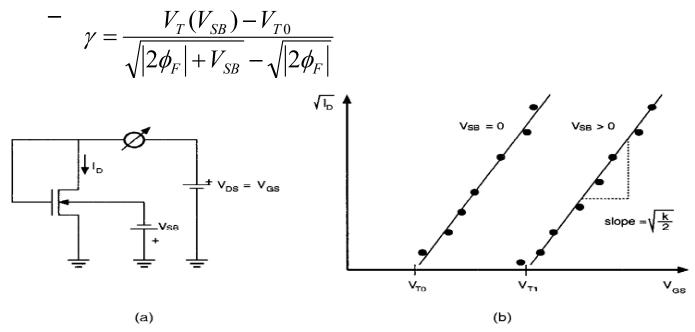

## Measurement of parameters- $\lambda$

- The voltage  $V_{GS}$  is set to  $V_{T0}$ +1

- The voltage V<sub>DS</sub> is chosen sufficiently large (V<sub>DS</sub>>V<sub>GS</sub>-V<sub>T0</sub>) that the transistor operates in the saturation mode, V<sub>DS1</sub>, V<sub>DS2</sub>

- $I_{D(sat)}-(k_n/2)(V_{GS}-V_{T0})^2(1+\lambda V_{DS})$  Since  $V_{GS}=V_{T0}+1 \Rightarrow I_{D2}/I_{D1}=(1+\lambda V_{DS2})/(1+\lambda V_{DS1})$

- Which can be used to calculate the channel length modulation coefficient  $\lambda$

- This is in fact equivalent to calculating the slope of the drain current versus drain • voltage curve in the saturation region

- The slope is  $\lambda k_{\rm p}/2$

(a) Test circuit arrangement and (b) measured data for experimental Figure 3.23 determination of the channel length modulation coefficient  $\lambda$ .

Measured voltage and current data for a MOSFET are given below. Determine the type of the device, and calculate the parameters  $k_n$ ,  $V_{T0}$ , and  $\gamma$ . Assume  $\phi_F = -0.3$  V.

#### Example 5

| V <sub>GS</sub> (V) | $V_{DS}(\mathbf{V})$ | V <sub>SB</sub> (V) | $I_D(\mu \mathbf{A})$ |

|---------------------|----------------------|---------------------|-----------------------|

| 3                   | 3                    | 0                   | 97                    |

| 4                   | 4                    | 0                   | 235                   |

| 5                   | 5                    | 0                   | 433                   |

| 3                   | 3                    | 3                   | 59                    |

| 4                   | 4                    | 3                   | 173                   |

| 5                   | 5                    | 3                   | 347                   |

First, the MOS transistor is on  $(I_D > 0)$  for  $V_{GS} > 0$  and  $V_{DS} > 0$ . Thus, the transistor must be an n-channel MOSFET. Assume that the transistor is enhancement-type and, therefore, operating in saturation mode for  $V_{GS} = V_{DS}$ . Neglecting the channel length modulation effect, the saturation mode current is written as

$$I_D = \frac{k_n}{2} \cdot (V_{GS} - V_T)^2 \quad \Leftrightarrow \quad \sqrt{I_D} = \sqrt{\frac{k_n}{2}} \cdot (V_{GS} - V_T)$$

Let  $(V_{GS1}, I_{D1})$  and  $(V_{GS2}, I_{D2})$  be any two current-voltage pairs obtained from the table. Then, the square-root of the transconductance parameter  $k_n$  can be calculated.

$$\sqrt{\frac{k_n}{2}} = \frac{\sqrt{I_{D1}} - \sqrt{I_{D2}}}{V_{GS1} - V_{GS2}} = \frac{\sqrt{433 \ \mu \text{A}} - \sqrt{97 \ \mu \text{A}}}{5 \ \text{V} - 3 \ \text{V}} = 5.48 \times 10^{-3} \ \text{A}^{1/2}/\text{V}$$

Thus, the transconductance parameter of this n-channel MOSFET is:

$$k_n = 2 \cdot (5.48 \times 10^{-3})^2 = 60 \times 10^{-6} \text{ A/V}^2 = 60 \ \mu \text{ A/V}^2$$

The extrapolated threshold voltage  $V_{T0}$  at zero substrate bias can be found by calculating the x-axis intercept of the square-root of  $(I_D)$  versus  $V_{GS}$  curve.

$$V_{T0} = V_{GS} - \sqrt{\frac{2 \cdot I_D}{k_n}} = 1.2 \text{ V}$$

To find the substrate bias coefficient  $\gamma$ , we must first determine the threshold voltage  $V_T$  at the source-to-substrate voltage of 3 V. Using one of the current-voltage data pairs corresponding to  $V_{SB} = 3$  V,  $V_T$  can be calculated as follows:

$$V_T(V_{SB} = 3 \text{ V}) = V_{GS} - \sqrt{\frac{2 \cdot I_D}{k_n}} = 4 \text{ V} - \sqrt{\frac{2 \cdot 173 \ \mu\text{A}}{60 \ \mu\text{A/V}^2}} = 1.6 \text{ V}$$

Finally, the substrate bias coefficient is found as:

$$\gamma = \frac{V_T (V_{SB} = 3 \text{ V}) - V_{T0}}{\sqrt{|2\phi_F| + V_{SB}} - \sqrt{|2\phi_F|}} = \frac{1.6 \text{ V} - 1.2 \text{ V}}{\sqrt{0.6 \text{ V} + 3 \text{ V}} - \sqrt{0.6 \text{ V}}} = 0.36 \text{ V}^{1/2}$$

28